咱们最近发布了在PyTorch生态系统中启用IBM Spyre加快器的2026年上半年道路图。在配套的时期讲解中,咱们先容了该硬件的秉性——32个活跃AI中枢、夹杂精度SIMD-脉动阵列以及可编程数据流联想。

在这里,咱们思详实先容道路图的关键主题,以及咱们如安在一个主要由GPU塑造的生态系统中为数据流加快器构建一流的PyTorch撑握。咱们的理念是生态优先——咱们诓骗上游机制,最小化自界说代码,并回馈那些让下一个加快器更容易解任调换旅途的组件。

膨胀Inductor以撑握数据流概括

咱们正在树外膨胀inductor,以处理数据流加快器所需的概括。三个膨胀最为进击:率先,咱们引入了基于块的张量布局,使编译器概况推理Spyre环形集中中枢所守望的块结构数据出动。其次,咱们添加了多核职责分裂过程,在编译时间而非运转时将块分拨到Spyre的32个中枢上。第三,咱们添加了暂存器优化——Spyre中枢使用显式不停的片上内存而非硬件缓存,inductor在诊治数据时需要磋议这少许。这些膨胀将使torch.compile概况为咱们2026年上半年范围内的每个优先模子生成高效的Spyre代码,从Llama 3.1 8B到Granite 4 Hybrid 30B。

后端编译器中间暗示的两阶段方法

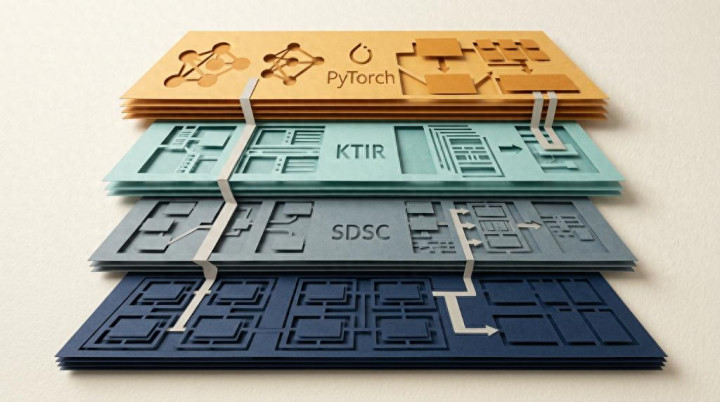

咱们对位于inductor高档图和Spyre机器码之间的后端编译器中间暗示遴荐两阶段方法。

在第一阶段,SuperDSC(SDSC)将动作后端编译器中间暗示——通盘操作左迁和代码生成的单一进口点。咱们优先模子所需的每个torch操作王人不错在SDSC中抒发,在PyTorch集成层和硬件特定优化之间提供明晰的分离。

在第二阶段,咱们将过渡到KernelTile IR(KTIR),这是一个更恰当社区的措施,与TileIR等新兴缱绻愈加一致。KTIR将泛化块级暗示,使其他数据流加快器——不单是是Spyre——不错将其用于更初级别的诊治和代码生成。咱们缱绻在本年上半年发布完好的KTIR措施,而况咱们正在联想的开源诊治算法不错适当咱们我方硬件以外的应用。

征战集成与分散式通讯

Spyre将十足通过树外膨胀注册为PyTorch征战:征战生命周期、内存不停、数据传输和诊治。咱们的谋略所以这种方式处理100%的注册,与径直征战看望比较支拨低于5%。咱们缱绻将构建的通用原语回馈到PyTorch中枢的OpenReg测试基础门径中。

对于多卡推理,咱们通过torch.inductor编译功能性荟萃操作(all-reduce、all-gather),这将使咱们在2026年上半年兑现通盘优先模子的分散式推理。遥远来看,咱们缱绻搬动到torch.distributed,开云体育并最终跟着社区通讯层的透露搬动到torch.comms。

出产推理与vLLM集成

出产推理将通过vLLM运转。咱们将Spyre动作vLLM平台插件启用,给与上游模子兑现而非爱戴咱们我方的分支。咱们的优先模子将通过Spyre上的vLLM进行端到端劳动。

两项优化将鼓吹实质可用性。新的Spyre严防力后端将摒除同质序列长度拘谨,径直减少Token间蔓延。上游vLLM中翻新的torch.compile工件缓存将把启动时刻降至几秒钟。咱们正在与vLLM社区相助,以透露平台插件接口。

测试与握续集成

咱们正在构建一个分层测试金字塔,将考证通盘堆栈:操作级正确性、inductor编译和左迁、模块级测试(包括严防力、归一化和激活)、顶层模子质地和性能,以及端到端vLLM推理。通盘测试王人将限度在优先模子范围内,并每晚运转,转头失败将在数小时内鲜艳。

咱们正在将此握续集成基础门径构建为对PyTorch生态系统的树外孝敬,建立其他加快器团队不错给与的模式。咱们的谋略是每晚运转的通过率跳跃95%,完好过程在三小时内完成。

回馈社区

生态优先意味着回馈,而不单是是在上头构建。本半年有三项特出孝敬:咱们缱绻上游OpenReg原语,使树外征战测试成为PyTorch的一流才能。咱们正在发奋将KTIR泛化为社区措施,使数据流加快器分享通用的块级中间暗示,而不是各自觉明我方的。咱们将纪录树外握续集成模式,使下一个加快器团队无须重新处分基础门径问题。

联想文档和RFC存放在咱们的各人存储库中。咱们迎接参与——不论是审查KTIR措施、试用Spyre追踪分析器,依然参与对于PyTorch原生加快器撑握应该是什么格局的接洽。

Q&A

Q1:IBM Spyre加快器有什么硬件特色?

A:IBM Spyre加快器领有32个活跃AI中枢、夹杂精度SIMD-脉动阵列以及可编程数据流联想。其中枢使用显式不停的片上内存而非硬件缓存,中枢之辗转纳环形集中架构,恰当块结构数据出动。

Q2:PyTorch奈何撑握Spyre这么的数据流加快器?

{jz:field.toptypename/}A:通过树外膨胀inductor来处理数据流加快器所需的概括,包括引入基于块的张量布局、添增加核职责分裂过程以及暂存器优化。Spyre将十足通过树外膨胀注册为PyTorch征战,处理征战生命周期、内存不停、数据传输和诊治,谋略是与径直征战看望比较支拨低于5%。

Q3:KTIR在Spyre的PyTorch撑握中演出什么扮装?

A:KTIR(KernelTile IR)是第二阶段的后端编译器中间暗示,它是一个更恰当社区的措施,与TileIR等新兴缱绻一致。KTIR将泛化块级暗示,使其他数据流加快器也不错将其用于更初级别的诊治和代码生成,而不单是劳动于Spyre硬件。